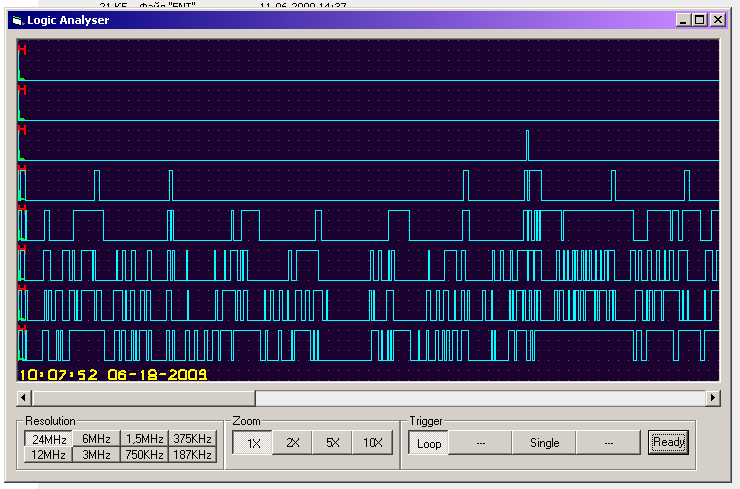

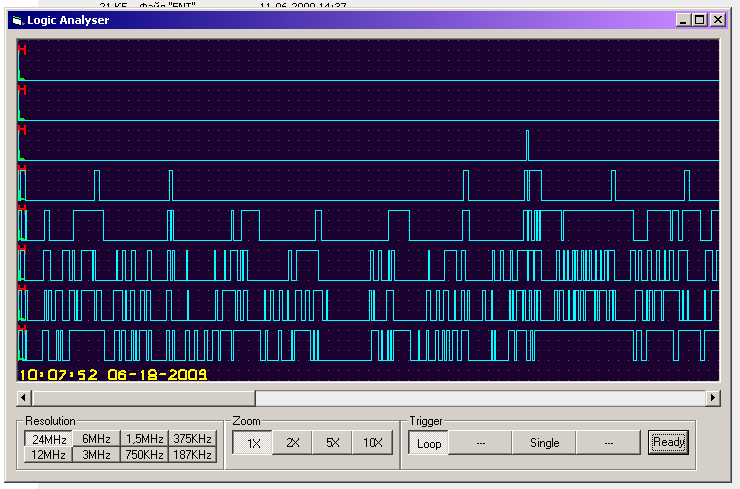

Для проверки работоспособности цифровой части была написана программа логического анализатора.

Исследуемые цифровые данные подаются на вход шинного формирователя вместо АЦП.

Исходник анализатора

Данная разработка задумывалась как дополнение к уже существующему аналоговому осциллографу для исследования редких и непериодических ВЧ сигналов. Она выполнена в виде приставки к ПК. При проектировании особое внимание уделялось доступности и низкой стоимости компонентов.

Железо:

Принцип работы цифрового осциллографа

достаточно простой. Необходимо быстро забить микросхему памяти данными,

а затем достаточно медленно передавать их по последовательному каналу в

компьютер для отображения и измерений.

Схема

генератора и делителя тактовой частоты

U1-генератор тактовой частоты 20МГц, его выход подключается к счетчику U2,U3. Коэффициент деления частоты 1...128 выбирается мультиплексором U4.

Схема запуска и формирования адреса

Мультиплексор U1 выбирает источник синхронизации: микропроцессор, компаратор уровня или внешний импульс. На U2 реализована схема запуска и останова преобразования. Когда система будет готова к новому приобразованию, то микроконтроллер подает разрешающий импульс на триггер U2A. При поступлении переднего фронта импульса синхронизации на тактирующий вход U2B коммутатор U3 переключается на тактовый сигнал и счетчик U4-U7 начинает перебирать адреса. Когда счетчик последовательно переберет весь диапазон адресов, то инвертором U8 будет сформирован сигнал сброса и отключения тактирования. В этот момент счетчик переключается коммутатором U3 на тактирование от контроллера для чтения и передачи данных в ПК.

Данные записываются в микросхему памяти

типа SRAM U1 UM61256K-15, которая была выдернута из материнки от 486-го

компьютера. При чтении микросхема памяти работает в режиме, управляемым

адресом. В этом режиме шинный формирователь U5 переходит в третье состояние

и запрещает прохождение цифровых сигналов от АЦП или от исследуемой схемы

в режиме логического анализатора. МК U4 формирует сигнал тактирования счетчика,

считывает содержимое микросхемы памяти и последовательно передает его в

ПК через UART. При записи выход памяти переходит в третье состояние(/OE=1),

U5 разрешает прохождение сигналов, а вход записи U1(/WE) тактируется основным

тактовым сигналом.

Данные в ПК передаются со скоростью 115200 бод. Поскольку

для передачи всего содержимого чипа памяти потребуется около трех секунд(32

килобайта), то предусмотрено 2 режима передачи: частичная передача(передается

1 килобайт, перемычка на выв. 1 U4 разомкнута) и полная передача(перемычка

замкнута). Первоначально задумывалось 2 канала ( PORTC

для второго чипа памяти), но пока я остановился на одном.

Схема

аналоговой части

На U1 реализован усилитель вертикального

отклонения. R5 и C2 подбираются по минимуму ВЧ звона. Надо сказать, что

в рекомендуемой схеме включения C2 отсутствует. Однако в ходе экспериментов

оказалось что его добавление улучшает переходные процессы. C4 подбирается

для уменьшения усиления и повышения стабильности на высоких частотах. Полоса

пропускания по уровню 0дб получилась 4МГц. Советские микросхемы идут с

очень большим разбросом параметров, поэтому требуется подбор экземпляра

U1 по минимальному времени установления и хорошей скорости нарастания.

Я пробовал в схеме быстрые ОУ LM318, которые по характеристикам вроде получше.

Но оказалось, что отобранный ОУ 574УД1 работает намного лучше, хотя у разных

микросхем LM318 частотные параметры весьма стабильны. Переменным резистором

RV3 регулируется смещение наблюдаемого сигнала вверх-вниз. На U2 собран

компаратор системы синхронизации. LM311 имеет время установления 200нс,

которого вполне достаточно для работы на частотах до 5-10 мегагерц. При

желании можно использовать и более быстродействующие компараторы. Резистором

RV1 устанавливается требуемый уровень синхронизации. В схеме применен быстрый(по

тем временам) советский параллельный АЦП К1107ПВ2(на схеме не показан).

Схема включения АЦП - стандартная из ДШ. Его можно

заменить на 1107ПВ1А с уменьшением разрядности до 6 бит(в случае с К1107ПВ1Б

максимальная скорость будет в 2 раза ниже - 10 мегавыборок/сек). Резистором

RV2 настраивается опорное напряжение --2 вольта для АЦП. Аналоговая часть

имеет незаконченный вид, здесь отсутствует защита от перенапряжения по

входу, защита АЦП, нет входного делителя и входное сопротивление не многим

более килоома. Впрочем это не мешает измерять низковольтные сигналы от

источников с малым выходным сопротивлением в десятки-сотни ом.

Двухполярный БП без особенностей. Только трансформатор следует выбирать достаточно мощный т.к. одна микросхема АЦП потребляет ток 0,5А.

Конструкция была собрана на трех макетных платах, никакие печатки не разрабатывались.

Софт:

Для проверки работоспособности цифровой

части была написана программа логического анализатора.

Исследуемые цифровые данные подаются

на вход шинного формирователя вместо АЦП.

Исходник

анализатора

Изначально я использовал готовый кварцевый генератор на 48 МГц. Эта частота делилась до 24МГц. Но после подключения АЦП я увидел что это для него многовато(кроме того схема не обеспечивает требуемую скважность тактового сигнала). В результате частота была понижена до паспортных 20МГц.

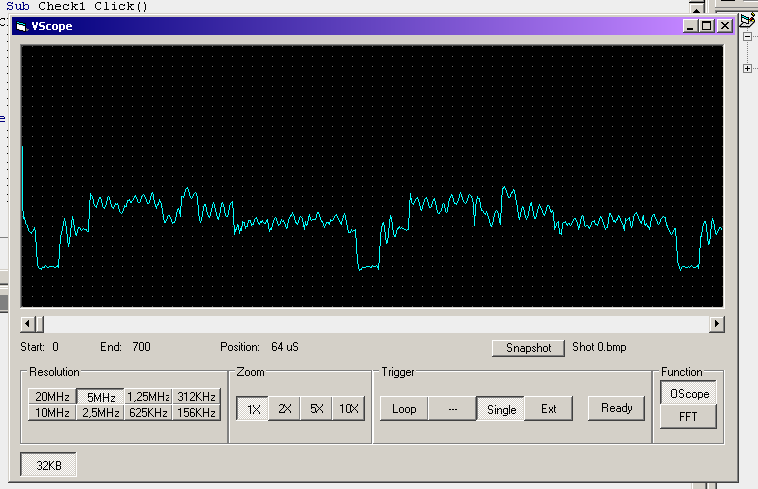

Программа цифрового осциллографа имеет

более продвинутый интерфейс. Здесь показаны несколько захваченных строк

видеосигнала PAL. Помимо всего прочего я добавил функцию анализатора спектра.

БПФ производится на 512 точек.

Реально можно наблюдать форму сигналов

с частотой где-то до 1/20-1/10 частоты дискретизации. Дальше уже начинает

появляться алиасинг и форма сигнала достаточно сильно искажается. Спектр

можно смотреть до 1/2 частоты дискретизации. Выше проявляется стробоскопический

эффект и спектр инвертируется.

Исходник

осциллографа

Протокол общения приставки с компьютером строится следующим образом. От ПК идут однобайтовые команды, управляющие работой. В сторону ПК - пакеты, размер которых определяется выбранным режимом. По окончании преобразования в ПК шлется пакет данных. Когда ПК обработает его и будет готов к приему нового, то он посылает в приставку команду начала нового преобразования.

Примечание. В ходе экспериментов схема неоднократно менялась и дорабатывалась. Хотя я и старался документировать изменения, но я не могу утверждать что схема 100% правильная. Вы можете использовать ее для понимания принципа работы системы. По этой же причине не рекомендуется браться за нее начинающим радиолюбителям.

Идеи по упрощению. Запихнуть всю цифровую часть на мелкой логике в какую-нибудь ПЛМ. Тогда все устройство будет включать в себя не более 8-10 корпусов. Я присмотрел подходящие по цене микросхемы семейства MAX3000 от ALTERA. Возможно, что скоро удастся поиграться и с ними.

Похожие проекты:

http://vereschagin.net/